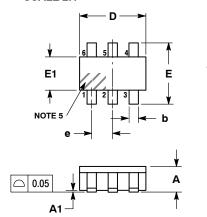

## TSOP-6 CASE 318G-02 **ISSUE V**

12

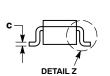

C SEATING PLANE

**DATE 12 JUN 2012**

## NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM

- MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D

- AND E1 ARE DETERMINED AT DATUM H.

PIN ONE INDICATOR MUST BE LOCATED IN THE INDICATED ZONE.

|     | MILLIMETERS |      |      |  |

|-----|-------------|------|------|--|

| DIM | MIN         | NOM  | MAX  |  |

| Α   | 0.90        | 1.00 | 1.10 |  |

| A1  | 0.01        | 0.06 | 0.10 |  |

| b   | 0.25        | 0.38 | 0.50 |  |

| С   | 0.10        | 0.18 | 0.26 |  |

| D   | 2.90        | 3.00 | 3.10 |  |

| E   | 2.50        | 2.75 | 3.00 |  |

| E1  | 1.30        | 1.50 | 1.70 |  |

| е   | 0.85        | 0.95 | 1.05 |  |

| L   | 0.20        | 0.40 | 0.60 |  |

| L2  | 0.25 BSC    |      |      |  |

| М   | 0°          | _    | 10°  |  |

**DETAIL Z**

Н

| STYLE 1: PIN 1. DRAIN 2. DRAIN 3. GATE 4. SOURCE 5. DRAIN 6. DRAIN | STYLE<br>PIN 1 |

|--------------------------------------------------------------------|----------------|

| STYLE 7:<br>PIN 1. COLLECTOR<br>2. COLLECTOR<br>3. BASE<br>4. N/C  | STYLE<br>PIN   |

COLLECTOR

6. EMITTER

2. SOURCE 2

3. GATE 2

4. DRAIN 2

5. SOURCE 1

DRAIN 1

STYLE 13: PIN 1. GATE 1

1. EMITTER 2 2. BASE 1 COLLECTOR 1 EMITTER 1 BASE 2 6. COLLECTOR 2

E 8: Vbus 2. D(in)

3. D(in)+ 4. D(out)+ 5. D(out) 6. GND 3. SOURO 5. DRAIN 6. HIGH VOLTAGE GATE

STYLE 14: PIN 1. ANODE SOURCE 3 GATE CATHODE/DRAIN CATHODE/DRAIN 5. CATHODE/DRAIN

3. R BOOST 4. Vz 5. V in 6. V out STYLE 9: PIN 1. LOW VOLTAGE GATE 2. DRAIN

STYLE 3: PIN 1. ENABLE 2. N/C

STYLE 15: PIN 1. ANODE SOURCE 3. GATE DRAIN 5. N/C

STYLE 16: PIN 1. ANODE/CATHODE 2. BASE 3 FMITTER 5. 6. CATHODE

STYLE 5: PIN 1. EMITTER 2 2. BASE 2 2. V in 3. NOT USED 4. GROUND 5. ENABLE 6. LOAD STYLE 10 PIN 1. D(OUT)+ 2. GND

STYLE 4: PIN 1. N/C

COLLECTOR

ANODE

CATHODE

3. D(OUT)-4. D(IN)-4 5. VBUS 6. D(IN)+

6. COLLECTOR 2 STYLE 11: PIN 1. SOURCE 1 2. DRAIN 2 DRAIN 2 SOURCE 2 5. GATE 1 6. DRAIN 1/GATE 2

3. COLLECTOR 1 4. EMITTER 1

BASE 1

STYLE 17: PIN 1. EMITTER

2. BASE

STYLE 12: 2. GROUND 3. I/O 4. I/O 6. I/O

STYLE 6: PIN 1. COLLECTOR 2. COLLECTOR

5. COLLECTOR 6. COLLECTOR

3 BASE 4. EMITTER

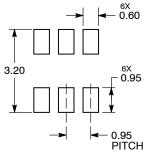

## RECOMMENDED **SOLDERING FOOTPRINT\***

**DIMENSIONS: MILLIMETERS**

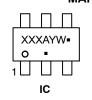

## **GENERIC** MARKING DIAGRAM\*

3 ANODE/CATHODE

CATHODE

COLLECTOR

XXX = Specific Device Code

= Pb-Free Package

= Date Code

XXX = Specific Device Code Α =Assembly Location

Υ = Year

W = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ", may or may not be present.

M

| DOCUMENT NUMBER: | 98ASB14888C | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | TSOP-6      |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.